单元测试

Arduino基础与进阶

《红宝石》

SDWAN

vr

特此声明

数维杯

PORT和PID区别

FANUC机器人

dockerfile

自动批量下载图片的插件

Semaphore

procast

断点

知识计算

网页模版html

Security

对象

web网页设计期末课程大作业

卡顿

内存屏障

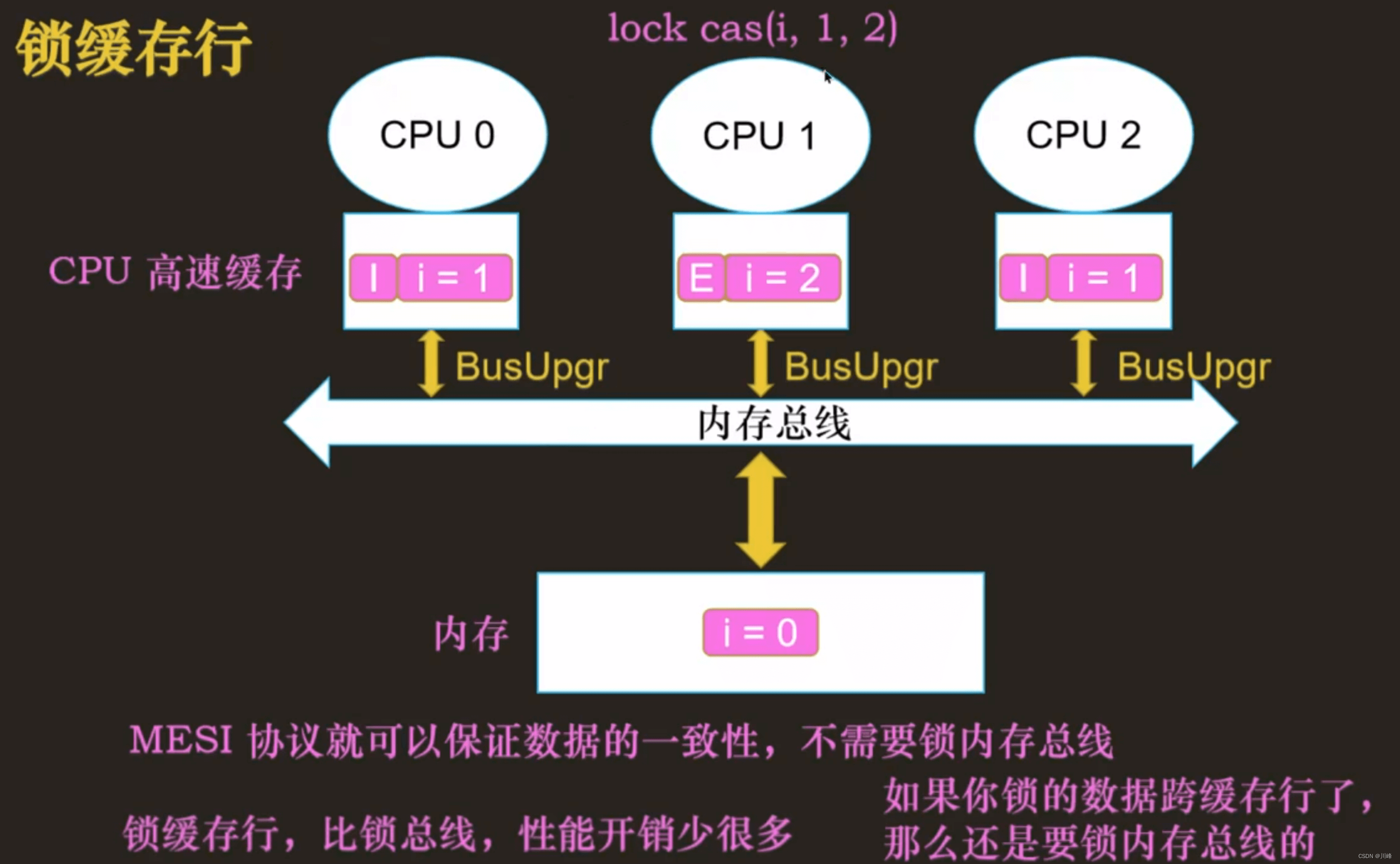

2024/4/14 14:50:44DPDK-同步互斥机制

0x01 缘由 继续学习DPDK设计思想。 0x02 概念 原子操作:多个线程执行一个操作时,其中任何一个线程要么完全执行完此操作,要么没有执行此操作的任何步骤,那么这个操作就是原子的。原子操作操作系统中:“不能被进一步分割…

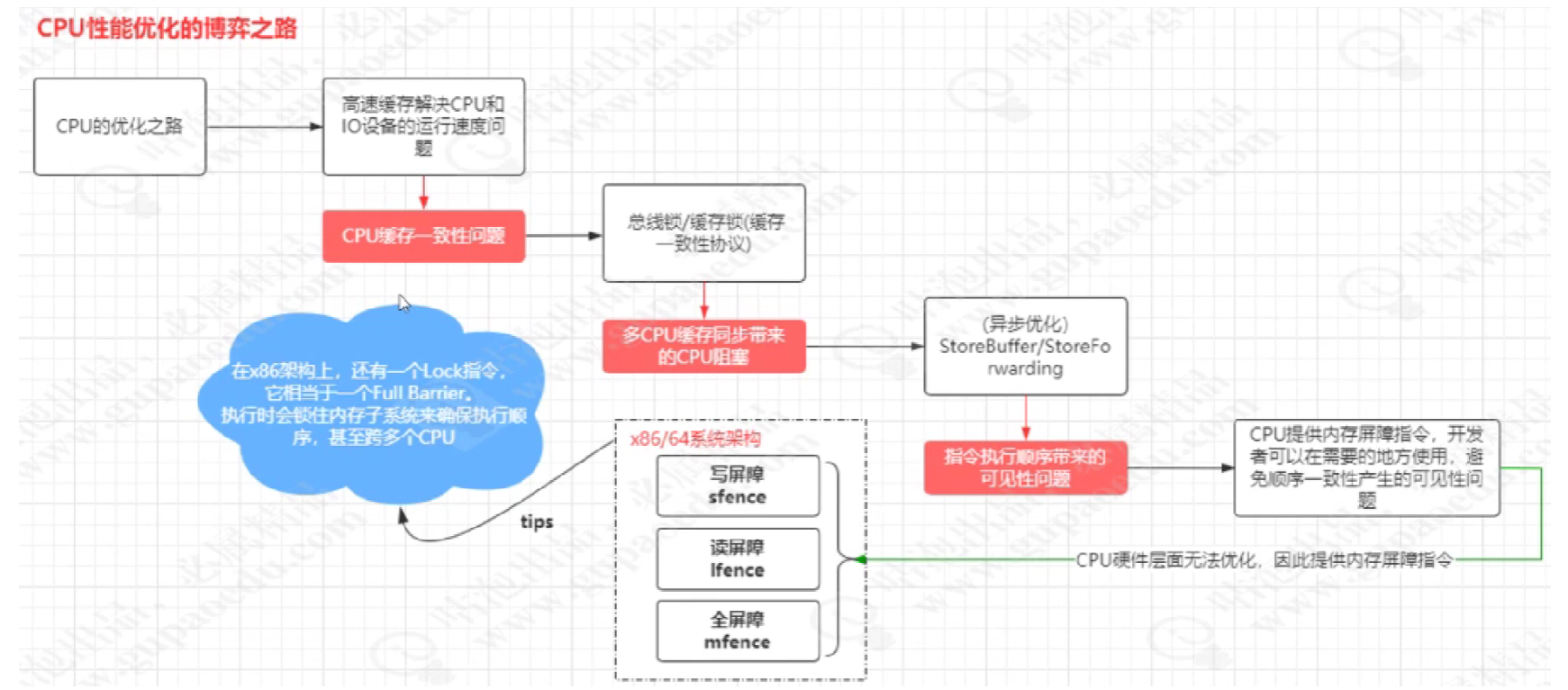

3_并发编程可见性(volatile)之缓存锁内存屏障过程

并发编程可见性volatile

1.背景原来

从下面的程序可以知道main线程把stop修改成false,而在t1线程没有中没有读取到stop值为false,所以导致了t1线程不能够停止。

从而说明stop值在线程t1不可见,解决这个问题在stop变量上添加volatile即可(p…

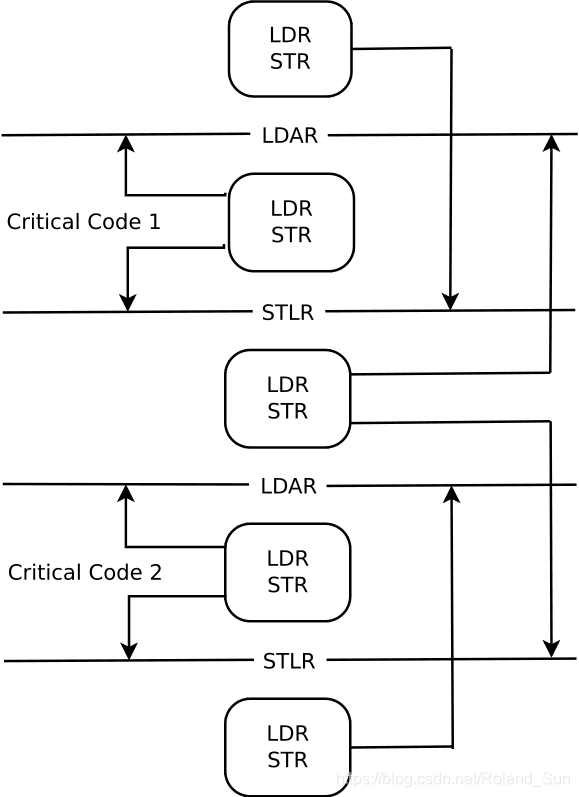

Java基础: 什么是指令重排序/as-if-serial/内存屏障/happens-before

Java基础知识

指令重排序

在执行程序时,为了提高性能,编译器和处理器会对指令做重排序。编译器优化重排序:编译器在不改变单线程程序语义的前提下,可以重新安排语句的执行顺序。指令级并行的重排序:如果不存l在数据依赖…

【JUC系列-01】深入理解JMM内存模型的底层实现原理

一,深入理解JMM内存模型

1,什么是可见性

在谈jmm的内存模型之前,先了解一下并发并发编程的三大特性,分别是:可见性,原子性,有序性。可见性指的就是当一个线程修改某个变量的值之后,…

keil、MDK、armcc 内存屏障语句

CMSIS 中定义为 __memory_changed

/* cmsis_armcc.h */#ifndef __COMPILER_BARRIER#define __COMPILER_BARRIER() __memory_changed()

#endif内存屏障语句:

__schedule_barrier();或者:

__memory_changed();等同于GCC的ÿ…

JVM第七讲:JVM 基础 - Java 内存模型详解

JVM 基础 - Java 内存模型详解 本文是JVM第七讲,JVM 基础 - Java 内存模型详解。主要转载自 Info 上深入理解Java内存模型, 作者程晓明。这篇文章对JMM讲的很清楚了,大致分三部分:1、重排序与顺序一致性;2、三个同步原语ÿ…

解密Linux内核神器:内存屏障的秘密功效与应用方法

一、内存屏障简介

现在大多数现代计算机为了提高性能而采取乱序执行,这可能会导致程序运行不符合我们预期,内存屏障就是一类同步屏障指令,是CPU或者编译器在对内存随机访问的操作中的一个同步点,只有在此点之前的所有读写操作都执…

JVM---Java内存屏障和JMM

Java内存屏障-JMMJava内存屏障和JMM硬件层数据一致性伪共享乱序问题如何保证特定情况下不乱序volatile的实现细节synchronized实现细节Java内存屏障和JMM

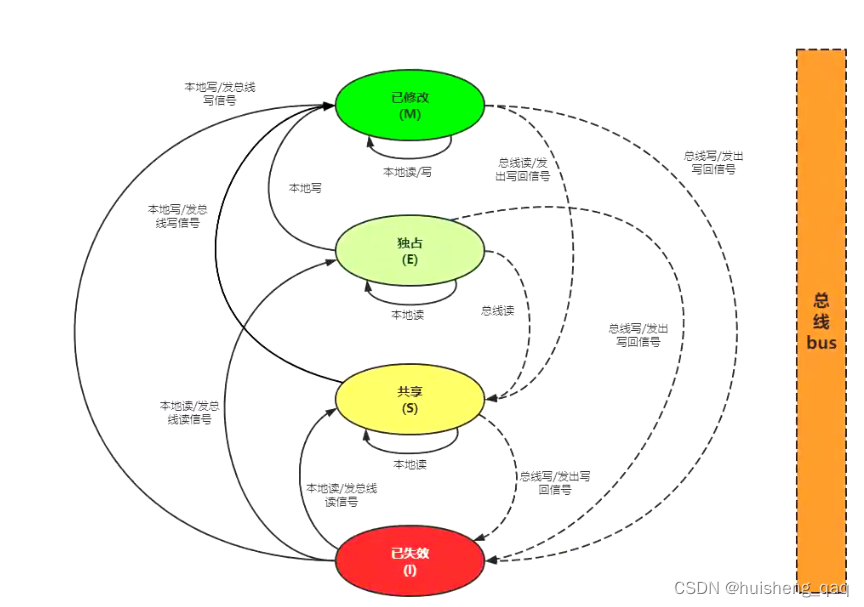

硬件层数据一致性

协议很多

intel 用MESI

https://www.cnblogs.com/z00377750/p/9180644.html

现代CPU的数据一致性实…

【0234】PgBackendStatus 记录当前postgres进程的活动状态

1. 关于PgBackendStatus

每个存活的后端进场在共享内存中维护一个PgBackendStatus结构体,显示其当前活动状态。(结构体是根据BackendId分配的,但这并不重要。)

请注意: 进场状态收集器进程不参与、甚至不访问这些结构。 每个辅助进程还在共享内存中维护一个PgBackendStatu…

理解Memory Barrier(内存屏障)

本文例子均在 Linux(g)下验证通过,CPU 为 X86-64 处理器架构。所有罗列的 Linux 内核代码也均在(或只在)X86-64 下有效。

本文首先通过范例(以及内核代码)来解释 Memory Barrier,然…

【操作系统笔记十】缓存一致性

CPU 核心之间数据如何传播

高速缓存中的值被修改了,那么怎么同步到内存中呢?

① 写直达(Write-Through)② 写回(Write-Back)

写直达(Write-Through) 简单,但是很慢&am…

mfence, lfence, sfence什么作用?

mfence, lfence, sfence什么作用?

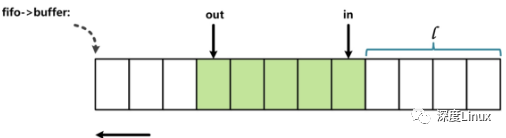

// src/backend/utils/rac/lock_free_queu.array_spsc_queue.c

#define mb() asm volatile("mfence":::"memory")

#define rmb() asm volatile("lfence":::"memory")

#define wmb() asm volatile(…